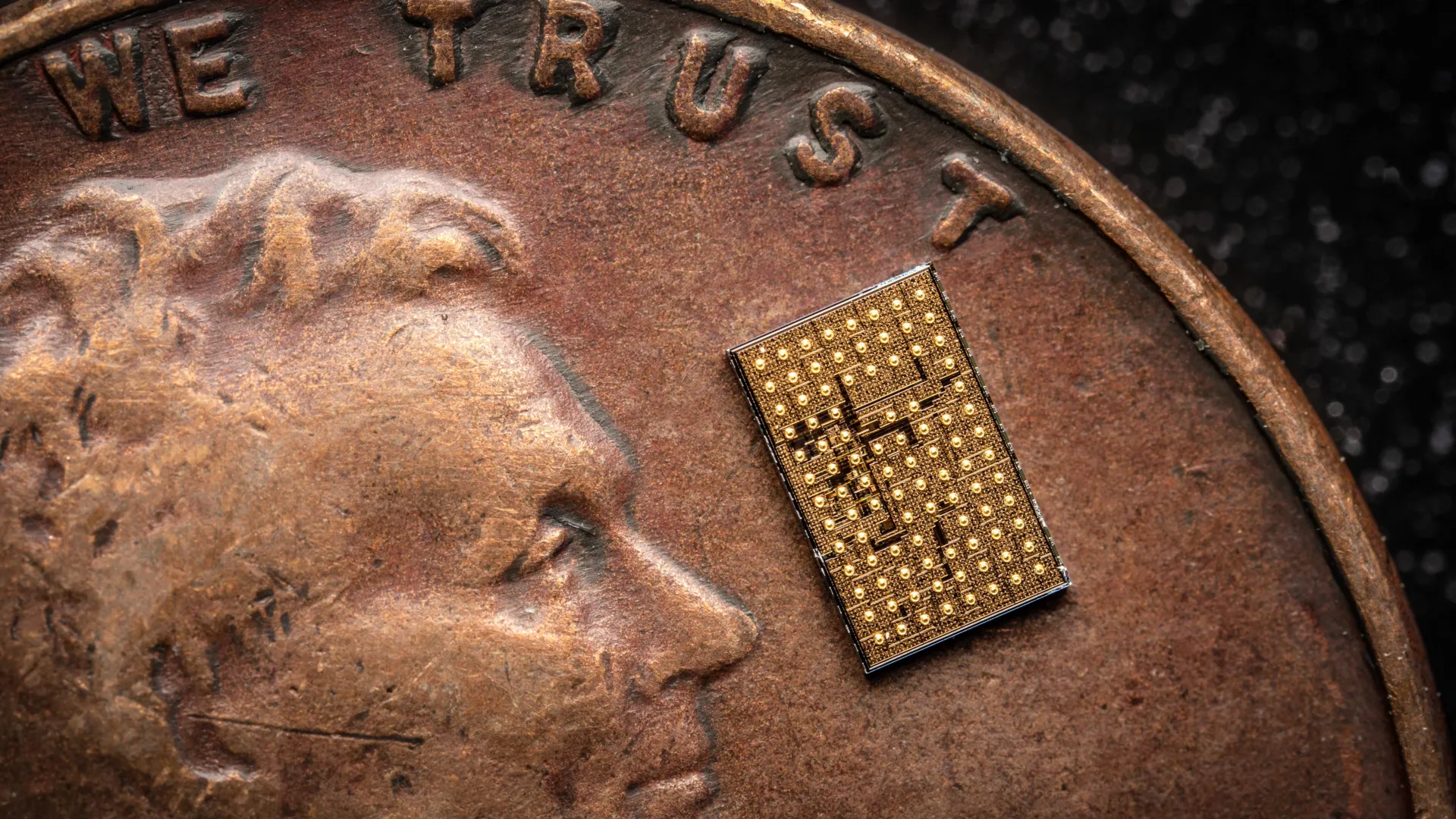

As the global digital infrastructure expands at an unprecedented rate, driven largely by the rapid proliferation of artificial intelligence and cloud computing, the energy demands of data centers have reached a critical juncture. To address the mounting pressure on power grids and the cooling requirements of high-performance computing hardware, engineers at the University of California San Diego have unveiled a breakthrough chip design that promises to significantly enhance the efficiency of power delivery to graphics processing units (GPUs). This innovation centers on a sophisticated redesign of the DC-DC step-down converter, a fundamental component responsible for translating high-voltage electricity into the lower levels required by sensitive silicon chips. In rigorous laboratory testing, a prototype of this hybrid chip demonstrated the ability to perform voltage conversion with remarkable efficiency under conditions that mirror the high-stress environments of modern data centers.

The research, recently published in the prestigious journal Nature Communications, marks a significant departure from decades-old power management paradigms. By moving away from traditional magnetic-based components and embracing a hybrid approach that utilizes piezoelectric resonators, the team led by the UC San Diego Jacobs School of Engineering has provided a potential blueprint for smaller, more energy-dense, and highly efficient computing systems. This development comes at a time when industry leaders are searching for ways to mitigate the environmental footprint of massive server farms while simultaneously pushing the boundaries of computational power.

The Evolution of Power Management in Advanced Computing

To understand the significance of the UCSD breakthrough, one must first consider the technical challenges inherent in modern power distribution. In the current data center architecture, electricity is typically distributed across the facility at 48 volts. This relatively high voltage is used to minimize energy loss during transmission across the vast network of racks and servers. However, the high-performance GPUs and CPUs that perform the actual calculations operate at much lower voltages, typically ranging between 1 and 5 volts.

The bridge between the 48-volt supply and the 1-volt requirement is the DC-DC step-down converter. For decades, these converters have relied on inductors—components that store energy in a magnetic field. While inductive converters have been refined to a high degree of reliability, they are increasingly becoming a bottleneck in the quest for miniaturization and extreme efficiency. As the gap between the input voltage (48V) and the output voltage (1-5V) widens, traditional inductive converters struggle to maintain efficiency. They lose significant amounts of energy as heat and require increasingly large physical footprints to handle the high currents demanded by modern AI accelerators.

The limits of this traditional technology have become a primary concern for hardware architects. As GPUs like those produced by NVIDIA and AMD become more power-hungry—some now exceeding 700 watts per chip—the "last mile" of power delivery on the motherboard has become a major source of energy waste. Professor Patrick Mercier, a senior author of the study and a faculty member in the Department of Electrical and Computer Engineering at UC San Diego, noted that the industry has reached a point of diminishing returns with inductive designs. According to Mercier, there is very little room left for improvement in traditional inductive technology to meet the escalating needs of future computing generations.

A Mechanical Shift: The Role of Piezoelectric Resonators

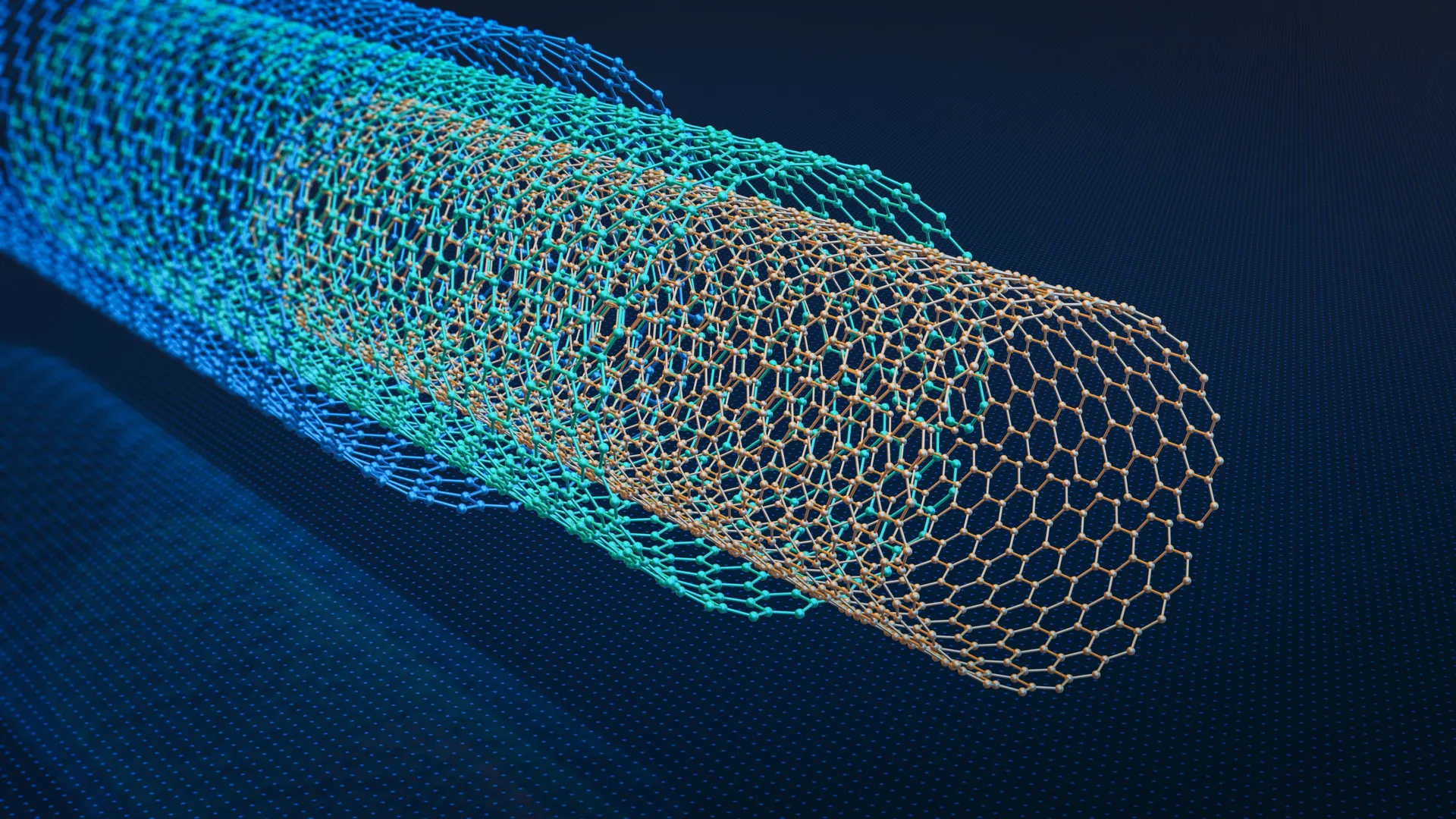

The UCSD team, which includes first author Jae-Young Ko, a doctoral student in electrical and computer engineering, turned to an alternative physical phenomenon: piezoelectricity. Unlike inductors that rely on magnetic fields, piezoelectric resonators store and transfer energy through mechanical vibrations. When an electric field is applied to a piezoelectric material, it physically deforms; conversely, mechanical stress on the material generates an electric charge.

This mechanical approach to energy storage offers several theoretical advantages over magnetism. Piezoelectric resonators can be manufactured in much smaller form factors than inductors while maintaining a high "Q factor," or quality factor, which is a measure of energy efficiency. Furthermore, because they do not rely on bulky copper coils or magnetic cores, they are potentially easier to integrate into modern semiconductor manufacturing processes.

However, historical attempts to use piezoelectric resonators in power converters have faced a recurring obstacle: they were often unable to deliver high levels of power or maintain efficiency when subjected to large voltage conversion ratios. Specifically, when trying to drop 48 volts down to the low single digits, previous piezoelectric designs would suffer from excessive energy loss and limited current output, making them impractical for the high-current demands of a GPU.

The Hybrid Innovation: Combining Piezoelectrics and Capacitors

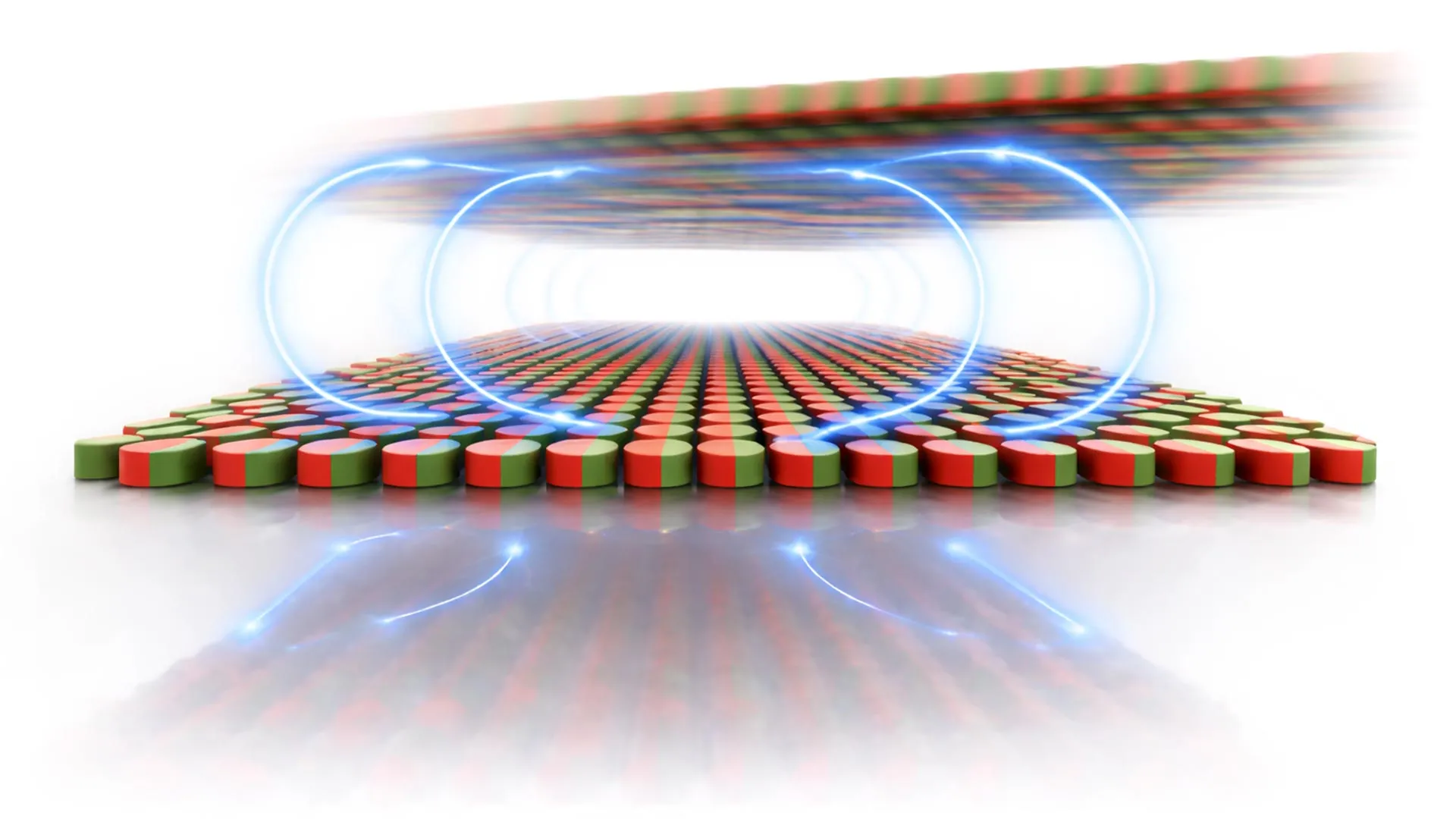

The breakthrough achieved by the UC San Diego researchers lies in a "hybrid" topology. Rather than relying solely on the piezoelectric resonator to handle the entire voltage drop, the team integrated the resonator with a series of small, commercially available capacitors. These components are arranged in a specific, proprietary configuration that allows the system to partition the voltage drop across multiple stages.

This hybrid architecture creates multiple pathways for energy to flow through the converter. By distributing the electrical stress, the design reduces the burden on the piezoelectric resonator, allowing it to operate within its "sweet spot" of maximum efficiency. The capacitors act as supplementary energy reservoirs, smoothing the power delivery and enabling the system to handle significantly higher currents than previous all-piezoelectric designs.

The prototype chip developed by the team was subjected to rigorous testing to validate these theoretical benefits. The results were highly encouraging. The device successfully converted a 48-volt input down to 4.8 volts—a standard intermediary step in data center power delivery—with a peak efficiency of 96.2 percent. Perhaps more importantly for data center applications, the chip was able to deliver approximately four times more output current than any previous piezoelectric-based converter design. This increased current density is crucial for powering modern processors that require hundreds of amps of current at very low voltages.

Chronology and Research Context

The development of this hybrid converter did not happen in isolation but is the result of several years of targeted research at the UC San Diego Jacobs School of Engineering. The project was supported in part by the Power Management Integration Center (PMIC), an Industry-University Cooperative Research Center (IUCRC) funded by the National Science Foundation (NSF). The PMIC serves as a bridge between academic innovation and industrial application, ensuring that research projects are aligned with the real-world needs of the electronics industry.

The timeline of the research highlights a steady progression from fundamental material science to integrated circuit design:

- Phase 1 (Fundamental Research): Investigation into the properties of piezoelectric materials at high frequencies and their behavior under high electrical loads.

- Phase 2 (Topology Design): The conceptualization of the hybrid capacitor-piezoelectric circuit to overcome the power density limits of pure piezoelectric converters.

- Phase 3 (Prototyping): The fabrication of the custom integrated circuit (IC) and the assembly of the prototype converter.

- Phase 4 (Testing and Validation): Extensive laboratory trials measuring efficiency, thermal performance, and current delivery under simulated data center loads.

- Phase 5 (Publication): The peer-reviewed release of the findings in Nature Communications in late 2024.

Industry Implications and the AI Boom

The timing of this innovation is particularly relevant given the current state of the global technology market. The "AI arms race" has led to a massive surge in the construction of data centers, with companies like Microsoft, Google, and Amazon investing tens of billions of dollars in infrastructure. Estimates from the International Energy Agency (IEA) suggest that data center electricity consumption could double by 2026, reaching levels comparable to the entire energy consumption of countries like Germany or Japan.

In this context, even a 1 or 2 percent increase in power conversion efficiency translates into massive cost savings and a significant reduction in carbon emissions. Furthermore, as data centers become more crowded, the physical size of power components becomes a limiting factor. The ability to shrink the power delivery system using UCSD’s hybrid design could allow for more GPUs to be packed into a single server rack, effectively increasing the computational density of the facility.

Industry analysts suggest that if this technology can be successfully commercialized, it could disrupt the multi-billion-dollar power management integrated circuit (PMIC) market. Traditional players in this space, who have long relied on silicon-based inductive switching regulators, may need to pivot toward hybrid or piezoelectric technologies to remain competitive in the high-performance computing sector.

Challenges on the Path to Commercialization

Despite the record-breaking performance of the prototype, Professor Mercier and his team are realistic about the hurdles that remain. Transitioning a laboratory breakthrough into a mass-produced industrial product involves solving complex engineering problems related to manufacturing and long-term reliability.

One of the most significant challenges involves the physical nature of the piezoelectric resonator. Because these devices function by vibrating at high frequencies, they cannot be attached to a printed circuit board (PCB) using traditional soldering methods. Standard solder creates a rigid bond that would dampen the vibrations, effectively "killing" the resonator’s ability to transfer energy. This necessitates the development of new packaging and integration strategies, such as specialized acoustic mounts or flexible interconnects, that allow the resonator to move freely while maintaining a stable electrical connection.

Additionally, the long-term durability of piezoelectric materials under the constant mechanical stress of data center operation must be thoroughly vetted. Data center components are expected to run 24/7 for several years without failure. Future research will focus on refining the materials used in the resonators and improving the overall circuit packaging to ensure they can withstand the rigors of industrial use.

Conclusion and Future Outlook

The hybrid piezoelectric converter developed at UC San Diego represents a bold step toward the next generation of power electronics. By successfully merging the high efficiency of mechanical resonators with the versatility of capacitive circuits, the researchers have opened a new "trajectory for improvement" in a field that many thought had reached its peak.

As the team continues to refine the design, the focus will shift toward further increasing the power density and exploring even higher voltage conversion ratios. The ultimate goal is to create a plug-and-play solution that can seamlessly replace existing inductive converters in the power delivery chains of GPUs and other high-performance processors.

While it may be several years before piezoelectric-based converters are found in every server rack, the UCSD prototype has proven that the "magnetic limit" is not an unbreakable ceiling. As digital demands continue to grow, such innovations will be essential to ensuring that the world’s computing power can expand sustainably, efficiently, and reliably. The project remains a centerpiece of the Power Management Integration Center’s portfolio, signaling a continued commitment to solving the most pressing energy challenges of the digital age.

Leave a Reply