The global surge in artificial intelligence, cloud computing, and large-scale data processing has placed an unprecedented strain on the world’s energy infrastructure. As data centers expand to accommodate the massive computational requirements of modern graphics processing units (GPUs), the efficiency of power delivery systems has become a primary concern for engineers and environmentalists alike. Addressing this challenge, researchers at the University of California San Diego (UC San Diego) have developed a groundbreaking hybrid chip design that leverages piezoelectric resonators to convert high-voltage electricity into the low-voltage levels required by advanced computing hardware. This innovation, recently detailed in the journal Nature Communications, represents a significant departure from traditional magnetic-based power conversion, offering a pathway toward smaller, cooler, and more energy-efficient data centers.

The Critical Challenge of Powering the AI Era

In the contemporary digital landscape, data centers serve as the backbone of the global economy. However, these facilities are notoriously energy-intensive, consuming an estimated 1% to 2% of the world’s total electricity—a figure projected to rise sharply as AI models become more complex. A significant portion of this energy is lost not during the computation itself, but during the process of power distribution and conversion.

Modern data center architectures typically distribute power at 48 volts (V) to minimize resistive losses along the distribution lines. However, the high-performance GPUs and CPUs that perform the actual processing operate at much lower voltages, often ranging between 1V and 5V. Bridging this gap requires highly efficient DC-DC step-down converters. As the demand for current increases—with some high-end AI chips drawing hundreds of amperes—the limitations of conventional power conversion technologies have become a major bottleneck in system design.

The Evolution and Limits of Traditional Power Conversion

For decades, the industry has relied on inductive DC-DC converters. These devices use inductors—components that store energy in magnetic fields—to manage voltage stepping. While inductive technology is mature and highly refined, it is approaching its physical limits. Inductors are inherently bulky and difficult to integrate directly onto silicon chips, often requiring significant space on printed circuit boards (PCBs).

As engineers strive to make computing systems more compact and powerful, the size of these magnetic components has become a liability. Furthermore, when the gap between the input voltage (48V) and the output voltage (1-5V) is wide, the efficiency of traditional buck converters tends to plummet. This inefficiency manifests as heat, which necessitates additional energy for cooling systems, creating a cycle of waste that hampers the scalability of high-density server racks.

Patrick Mercier, a professor in the Department of Electrical and Computer Engineering at the UC San Diego Jacobs School of Engineering and the study’s senior author, noted that the industry has reached a plateau. "We’ve gotten so good at designing inductive converters that there’s not really much room left to improve them to meet future needs," Mercier explained. This realization prompted the research team to explore alternative physical mechanisms for energy storage and transfer.

Exploring Piezoelectric Resonators as a Disruptive Alternative

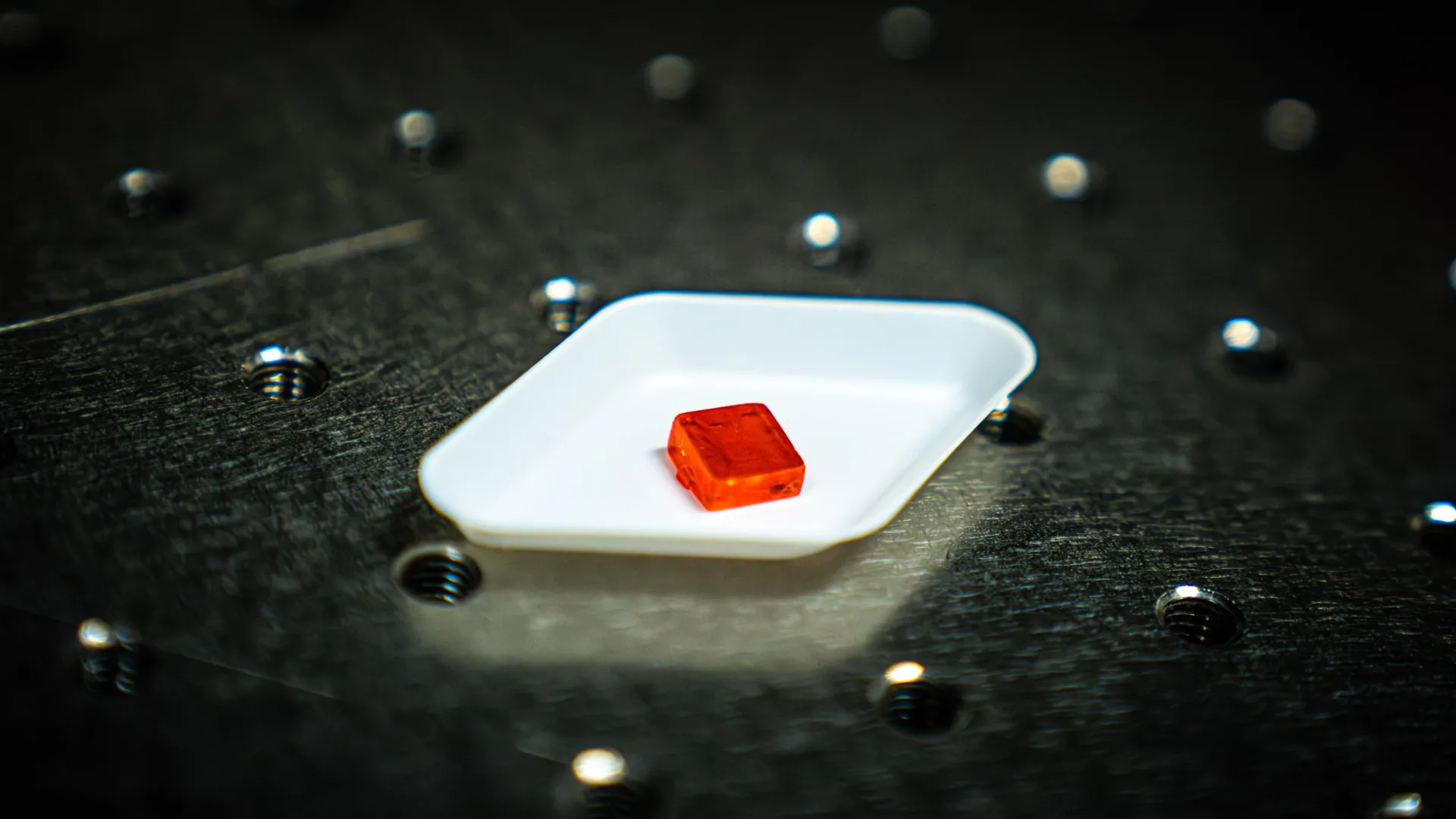

To bypass the constraints of magnetism, the UC San Diego team, led by Ph.D. student Jae-Young Ko, turned to piezoelectricity. Piezoelectric resonators are materials that generate an electric charge when subjected to mechanical stress and, conversely, vibrate when an electric field is applied. Unlike inductors, which store energy in magnetic fields, piezoelectric resonators store energy through mechanical vibrations.

These components offer several theoretical advantages over traditional inductors:

- Higher Energy Density: Piezoelectric materials can store more energy in a smaller volume than magnetic materials.

- Scalability: They are easier to manufacture at the micro-scale, potentially allowing for more integrated "power-on-chip" solutions.

- Reduced Electromagnetic Interference (EMI): Since they do not rely on magnetic fields, they produce less interference with surrounding sensitive circuits.

Despite these benefits, historical attempts to use piezoelectric resonators in high-power DC-DC converters have faced significant hurdles. Most notably, they struggled to maintain high efficiency when handling the large step-down ratios required by data centers, and they often failed to provide the high current levels necessary for modern GPUs.

The Hybrid Breakthrough: Combining Piezoelectrics and Capacitors

The UC San Diego researchers overcame these historical limitations by developing a "hybrid" architecture. Rather than relying solely on the piezoelectric resonator, the new design integrates the resonator with a network of small, commercially available capacitors.

This hybrid configuration creates a multi-stage conversion process within a single system. The capacitors help manage the initial voltage reduction and stabilize the flow of electricity, while the piezoelectric resonator handles the high-frequency energy transfer with minimal loss. This synergy allows the system to manage a 48V to 4.8V conversion—a tenfold reduction—without the precipitous drop in efficiency typically seen in other designs.

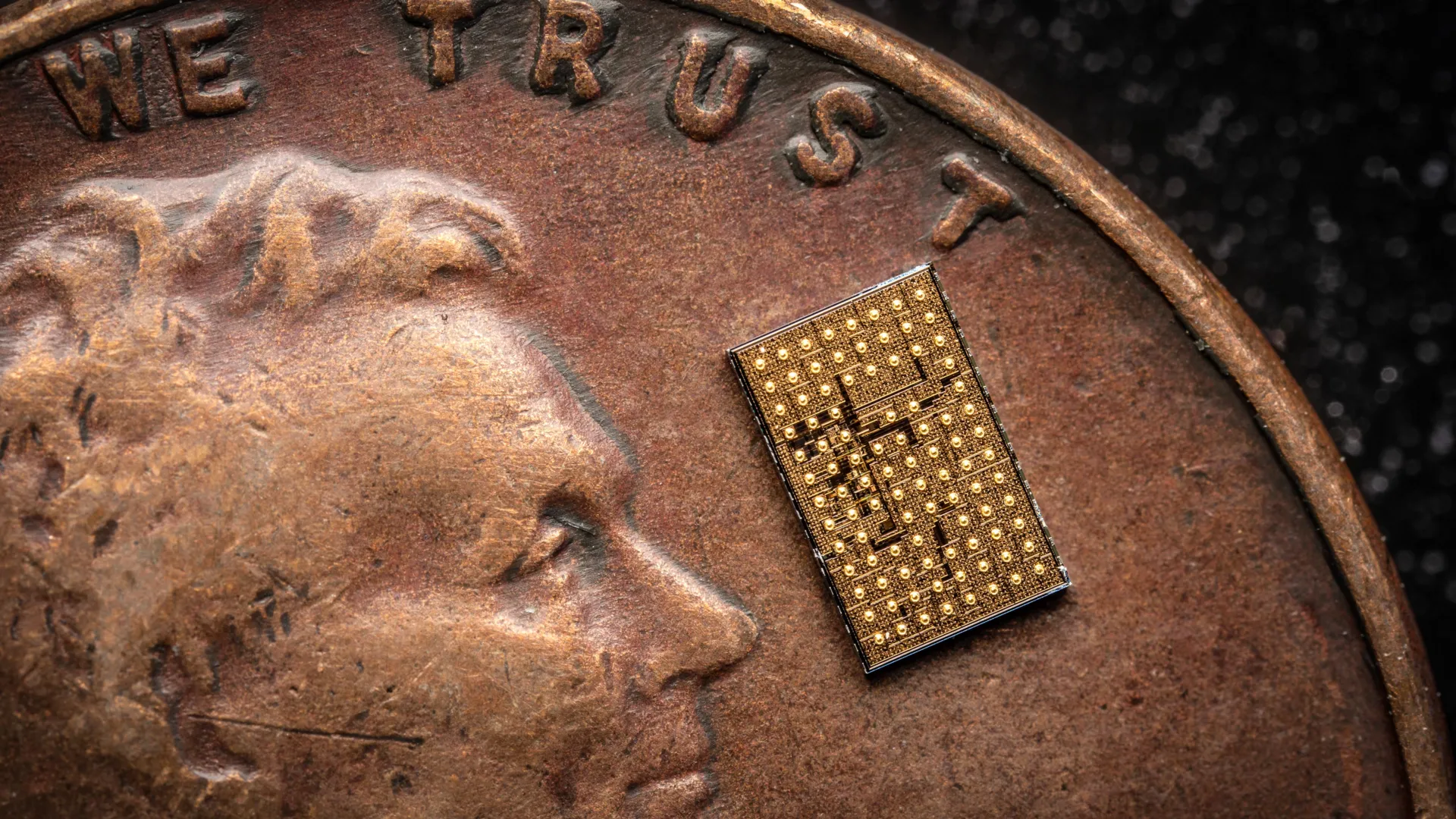

In laboratory testing, the prototype chip demonstrated a peak efficiency of 96.2%. This is a remarkable figure for a non-traditional converter operating at such a high step-down ratio. Furthermore, the design achieved a power density and output current roughly four times higher than previous piezoelectric-based attempts, proving that the technology can scale to meet the demands of industrial-grade hardware.

Detailed Performance Data and Experimental Results

The researchers’ findings, published in Nature Communications, provide a comprehensive data set comparing the hybrid design against both traditional inductive converters and previous piezoelectric models.

Key metrics from the study include:

- Voltage Range: The device was optimized for a 48V input, the standard for modern "Open Compute Project" data center racks.

- Efficiency: Peak efficiency reached 96.2% at a 4.8V output. Even under varying load conditions, the efficiency remained high, which is critical for real-world applications where GPU power draw fluctuates rapidly.

- Current Output: The hybrid design significantly increased the "current-handling capability," a common weak point for piezoelectric devices. By distributing the electrical load across multiple pathways involving both the resonator and the capacitors, the team reduced the mechanical strain on the piezoelectric material, allowing it to process more power without degrading.

- Form Factor: The prototype demonstrated that these components could be arranged in a footprint much smaller than the bulky inductors currently found in server power modules.

Overcoming Manufacturing and Integration Hurdles

While the laboratory results are promising, the transition from a prototype chip to a commercial product involves significant engineering challenges. One of the most prominent issues identified by the researchers is the physical nature of piezoelectric resonators. Because these devices function by vibrating at high frequencies, they cannot be attached to a circuit board using standard soldering techniques, which would dampen the vibrations and render the device useless.

"Piezoelectric-based converters aren’t quite ready to replace existing power converter technologies yet," Mercier cautioned. "But they offer a trajectory for improvement."

To address the integration issue, the team is currently researching new packaging methods. These include "flip-chip" bonding or specialized adhesive techniques that allow the resonator to remain mechanically "free" to vibrate while maintaining a solid electrical connection to the rest of the circuit. Additionally, future research will focus on the development of new piezoelectric materials that can operate at even higher temperatures and frequencies, further pushing the boundaries of what these chips can achieve.

Broader Industry Implications and Environmental Impact

The implications of this technology extend far beyond the laboratory. As tech giants like Google, Microsoft, and Amazon invest billions in AI infrastructure, even a 1% or 2% increase in power conversion efficiency can translate into hundreds of millions of dollars in saved electricity costs and a massive reduction in carbon footprints.

Furthermore, the smaller size of piezoelectric converters could allow for more compact server designs. In a data center, space is at a premium. By shrinking the power delivery components, engineers can fit more GPUs into a single rack, increasing the "compute density" of the facility. This is particularly relevant for "edge computing" applications, where powerful AI processing must be performed in constrained environments like autonomous vehicles or localized 5G base stations.

The shift toward 48V distribution is already a major trend in the industry, championed by the Open Compute Project (OCP). The UC San Diego design aligns perfectly with this roadmap, providing a technical solution for the most difficult part of the 48V architecture: the final step-down to the point-of-load (PoL).

Future Roadmap and Research Support

The development of the hybrid piezoelectric chip was supported in part by the Power Management Integration Center (PMIC), an Industry-University Cooperative Research Center (IUCRC) funded by the National Science Foundation (NSF). This partnership highlights the importance of collaboration between academia and industry in solving fundamental hardware challenges.

The research team has outlined a multi-year roadmap to bring this technology to maturity. The next phases of development will involve:

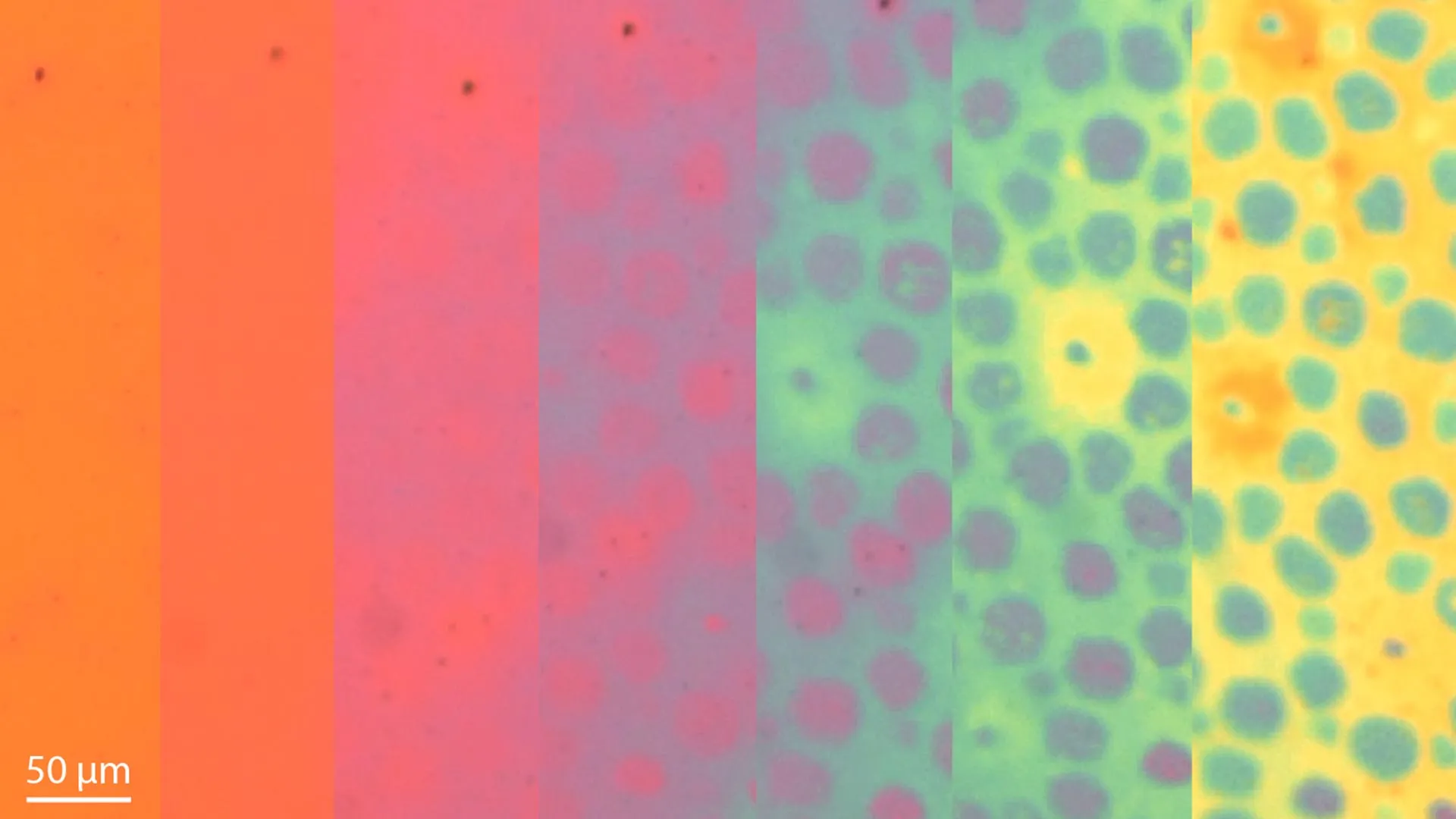

- Material Science: Testing new ceramic and single-crystal piezoelectric materials to find the optimal balance between durability and energy transfer.

- Circuit Optimization: Refining the capacitor network to further reduce the "switching losses" that occur during high-frequency operation.

- Packaging Innovation: Working with semiconductor packaging firms to create a standardized, manufacturable process for integrating vibrating resonators into standard chip sets.

As the industry approaches the "power wall"—the point where heat and energy consumption prevent further increases in processor speed—innovations like the UC San Diego hybrid chip may provide the necessary breakthrough to keep the AI revolution moving forward. While traditional magnets have served the electronics industry well for over a century, the future of high-performance computing may very well be built on the subtle vibrations of piezoelectricity.

Leave a Reply